WP1 - Embedded System Architectures

Objectives

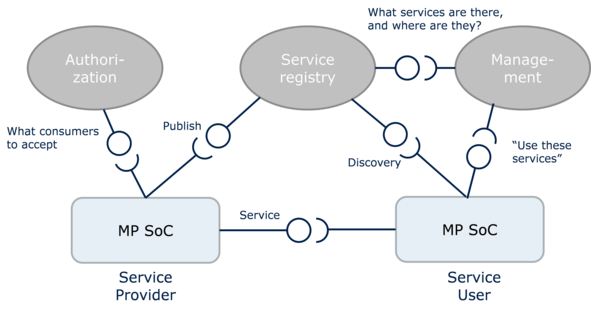

Focus of WP1 Embedded system architecture is an architecture enabling an open system of networked multi-core computation units. The open architecture is characterized by a set of (system) requirements, a set of constraints and a set of overall goals or objectives. On this architecture, classes of functional and non-functional services are to be run. This requires efforts in the fields of timing prediction, resource planning and assignment and adhering to existing standards.

Particularly the following objectives will be addressed:

- Interoperability and inerrability to the Internet through service interfaces

- Security regarding operation, maintenance and diagnosis through service interfaces

- Optimization of MCMC Power supply management in terms of power consumption and functional safety

- System dependability including services supporting functional safety and fault tolerance

- Enabling design and run time engineering, migration, configuration, deployment, maintenance and diagnoses of services executed at an MPSoC

- Service interface to service computation prioritization supporting issues like:

- Priorities of services with mixed criticalities

- Priorities of system resources usages e.g. power, core and memory availability

Our vision is to develop a service oriented framework enabling the construct of System-of-Systems based on networked MPSoCs in a systematic way, while preserving system properties like determinism, real-time performance, safety, security and fault tolerance and providing the possibilities for system validation, qualification and certification.

Work package structure

WP1 is structured into 6 Tasks:

Task 1.1 will address the integration of system functionalities at system service architecture level, based on service oriented architecture. Main objective is the investigation of state of the art and structuring of requirements from targeted application domains (EMC² Living Labs).

Particularly system aspects to be covered are

- system security, system safety,

- system service criticality capabilities,

- real time capabilities,

- energy usage and computation efficiency,

- system power supply efficiency and flexibility,

- AMSPS functionality and safety,

- system robustness and fault tolerance,

- performance predictability and

- variability adaptability.

Task 1.2 has the objective to develop a service architecture providing access to functional and non-functional properties for MPSoC hardware. It targets the migration from legacy systems and addressed the possibility of system certification considering IPR protection within MPSoCs.

In depth architecture definitions will be provided on the topics of

- service interoperability,

- system level convergence of real time capabilities,

- service and system security as well as on

- safety and fault tolerance concepts.

Task 1.3 will investigate system service interoperability. This will cover both MPSoC internal and external service interoperability. Interoperability will be addresses at protocol level, service semantics level and service description level.

Task 1.3 will lead to

- technology and methodologies enabling interoperability between services internal to an MPSoC

- technology and methodologies enabling service interoperability to external services and

- service descriptions enabling technology demonstrations in several of the Living labs.

Further, T1.3 will investigate variability in service functionality resource requirements and achieve possible means of predicting functionality quality.

Task 1.4 will analyse SoA architecture technologies regarding real time performance at system level. This will consider protocols, service semantics, computational and communication hardware, underlying software solutions used and requested by the EMC² Living Labs. T1.4 will lead to architectural components supporting mixed criticality operation and performance prediction to be integrated into the EMC² SoA architecture.

Task 1.5 targets identification of security goals in SoA for embedded systems and exploration of appropriate security services and related definitions of security services at service and system level. Security services will be evaluated according to the security requirements put forward by the use cases in the EMC² Living Labs.

Expected output of T1.5 are

- security service architectural block,

- service semantics and

- service descriptions

to be integrated to the SoA EMC² architecture.

Target of Task 1.6 is the identification of requirements and special challenges regarding functional safety in EMC² systems and SoA. Currently, applications are often statically scheduled as if they would be located at single cores. This task aims to develop more dynamic scheduling approaches, which are not supported or even prohibited by current safety standards. The aim of this is the harmonization of the new, advanced embedded system architecture with existing safety standards. This includes the investigation of phases in the safety lifecycle where EMC² systems require special considerations.

Multi-core systems do not only pose special requirements on certification but can also be used for surveillance and redundancy and thus support certification. One main challenge is to show the independence of elements required for ASIL decomposition as proposed for example in ISO 26262 for EMC² systems with shared memory spaces and for mixed criticality.